Architektura systemów komputerowych

Egzaminy i wykłady u dr. Drabowskiego (2014-2015)

Prowadzący prof. dr hab. inż. Sapiecha

Materiały:

ASK 2011 - Wykłady ask2011final.pdf

Tryby adresowania : adresowanie.pdf

Opracowanie: ask_-_opracowanie.pdf

ZADANIA:

\\

ZADANIE: sumowanie wektora, bez instrukcji ISZ, ale dodawanie ma autonastępnikowanie. 22pkt (5pkt)

ROZWIĄZANIE:

ORG 30 (określamy, gdzie zaczyna się wykonywanie instrukcji)

20 50 (adres wektora liczb)

21 -n (długość wektora)

22 suma

…

30 CLA (zerujemy akumulator)

31 STA 22 (zapisujemy wartość sumy do M[22])

32 LDA 22 (wczytujemy wartość sumy częściowej)

33 ADD, *, +, 20 (adres argumentu zapisany w M[20], zwiększamy po wykonaniu rozkazu zawartość M[20])

34 STA 22 (zapisujemy sumę częściową)

35 LDA 21 (ładujemy M[21] do akumulatora)

36 INC (zwiększamy zaw. akumulatora)

37 STA 21 (zapisujemy M[21])

38 SZA 21 (sprawdzamy czy M[21] jest {już} zerem, jeśli tak, wykona się SKIP, jeśli nie, @39)

38 SZA (Tak naprawde ta instrukcja sprawdza akumulator, a nie miejsce w pamieci, wiec linijka powyżej jest imho źle. W instrukcji wyżej jest tak zastosowane SZA jak mogłoby być ISZ. SZA jest bezadresowe - wojtek

39 BRA 32 (skok do @32)

40 … (dalsze instrukcje)

…

50 dane

…

50+(n-1)

\\

———————————————————————————————————

\\

ZADANIE:

Zaprojektuj operację PUSH i POP dla stosu, do którego będą zapisywane i odczytywane dane z rejestru A. (25pkt)

\\

ROZWIĄZANIE:

Przyjmujemy, że mamy następujące rejestry:

SP - wskaźnik stosu

SMAX - adres o 1 wyższy od ustalonej górnej wartości granicznej stosu

SMIN - adres o 1 niższy od ustalonej dolnej wartości granicznej stosu

\\

Wszystkie te rejestry mają po n bitów.

\\

warunki:

z = (SMAX[0] XNOR SP[0]) AND (SMAX[1] XNOR SP[1]) AND … AND (SMAX[n] XNOR SP[n])

czyli wartość SP ma być równa SMAX (stos pełny)

\\

x = (SMIN[0] XNOR SP[0]) AND (SMIN[1] XNOR SP[1]) AND … AND (SMIN[n] XNOR SP[n])

czyli wartość SP ma być równa SMIN (stos pusty)

\\

Zakładamy też, że do przerzutników z i x wartości zapisywane są tylko przed wykonaniem instrukcji PUSH i POP.

\\

PUSH:

C2t0(~z): MBR←A

C2t1(~z): SP←SP+1, PAO start zapis

C2t2(~z): M(SP)←MBR

C2t3(~z): F←0

\\

PUSH_v2:

C2t0(~z): MBR←A, SP←SP+1

C2t1(~z): MAR←SP, PAO start zapis

C2t2(~z): M←MBR

C2t3(~z): F←0

\\

POP

C2t0(~x): A←0, PAO start odczyt

C2t1(~x): MBR←M(SP), SP←SP-1

C2t2(~x): A←A+MBR

C2t3(~x): F←0

\\

POP_v2

\\

C2t0(~x): A←0, MAR←SP, PAO start odczyt

C2t1(~x): MBR←M, SP←SP-1

C2t2(~x): A←A+ MBR

C2t3(~x): F←0

\\

Przy *_v2 przyjmujemy, że mamy połączenie pozwalające przypisać SP do MAR

(biorąc pod uwagę możliwe różnice w ilości bitów SP i MAR, chyba że przyjmiemy,

że są takiej samej wielkości - co jest raczej najbardziej sensowne).

\\

———————————————————————————————————

ZADANIE: Przeprojektuj procesor z wykładu tak , że BRA 0 spowoduje wykonanie operacji SKIP z zapisem PC w

rejestrze A.

\\

ROZWIĄZANIE:

Wprowadzamy dodatkowy przerzutnik MZ , do którego przez 16-wejściową bramkę or , podpinamy część MBR.

W cyklu pobrania rozkazu w t3, zapisujemy do niego wyjście bramki i go zamykamy. W tym przypadku wartość

rejestr MZ wygląda tak : MBR = 0 → MZ = 0…….. MBR = 1 → MZ = 1

Czemu 16? 16 daje nam pełne bezpieczeństwo w t2 pobrania rozkazu MBR[0-3] zostaje zerowany, więc część

rozkazowa nic nam nie popsuje, a jednocześnie cała 16 daje nam odpowiedni wynik przy adresowaniu pośrednim.

\\

W tym wypadku instrukcje można zapisać w taki sposób:

c2q2t0(~MZ): PC ‹- PC + 1

c2q2t1(~MZ): MBR ‹- PC, A ‹ 0

c2q2t2(~MZ): A ‹- A + MBR

c2q2t3(~MZ): F← 0 , R←0

\\

———————————————————————————————————

\\

ZADANIE: ISZ 0,sprawdzic, zapis akumulatora w pc, kasowanie akumulatora, kasowanie sterowania

\\

ROZWIĄZANIE:

MZ tak jak w poprzednim zadaniu

\\

c2q6t0(~MZ): MBR←A

c2q6t1(~MZ): PC←MBR

c2q6t2(~MZ): A←0

c2q6t3(~MZ): F←0, R←0

\\

———————————————————————————————————

\\

ZADANIE: BRA 0 › ma skoczyć do miejsca z rejestru A (pośrednio i bezpośrednio)

\\

ROZWIĄZANIE:

DB: 16 bitowa bramka NOR, do ktorej podpinamy MBR, czyli wykrywa same 0

\\

t0 ~DB : PC < MBR

\\

bezposrednio

t0~p DB : MBR ← A

t1~p DB : PC ← MBR

\\

\\

posrednio:

t0 p DB : MBR ← A

t1 p DB : MAR ← MBR, PAO s/o

t1 p DB : MBR ← M

t2 p DB : PC ← MBR

\\

———————————————————————————————————

\\

ZADANIE: rozkaz JS, adresowanie pośrednie, gdzie adres składa się z samych jedynek ma wywołać pułapkę:

zapisać zawartość akumulatora do rejestru OUT i wywoływać przerwanie

\\

ROZWIĄZANIE 1:

\\

MZ to przerzutnik podlaczony do MBR wykrywajacy 1 (MBR0 & MBR1…)

\\

OUT to rejestr podlaczony do MBR (nie wiem czy taki jest, wiec go tworze)

\\

t0 p MZ: MBR ← A

t1 p MZ: OUT ← MBR, R ← 1

\\

ROZWIĄZANIE 2:

\\

t0: MAR ← MBR, PAO s/o

t1: MBR ← M

t2 MZ: MBR < A

t3 MZ: OUT ← MBR, R ← 1

\\

———————————————————————————————————

\\

ZADANIE: zaimplementować sprzętowy stos i dopisać do niego sterowanie.

\\

ROZWIĄZANIE:

\\

przyłączenie rejestru na 16 słów do MBR. Wskaźnik SP do chodzenia po stosie,

flagi z = stos pełny (SP = 1111) - czterowejściowy AND i

x = stos pusty(SP = 0000) - czterowejściowy NOR

\\

PUSH:

c2t0~z: MBR←A

c2t1~z: SP←SP+1, STOS start zapis

c2t2~z: STOS(SP)←MBR

c2t3~z: F←0

\\

POP:

c2t0~x: A←0, STOS start odczyt

c2t1~x: MBR←STOS(SP), SP←SP-1

c2t2~x: A←A+MBR

c2t3~x: F←0

\\

RESET:

\\

c2t0: SP←0

c2t1: -

c2t2: -

c2t3: F← 0

\\

\\

———————————————————————————————————

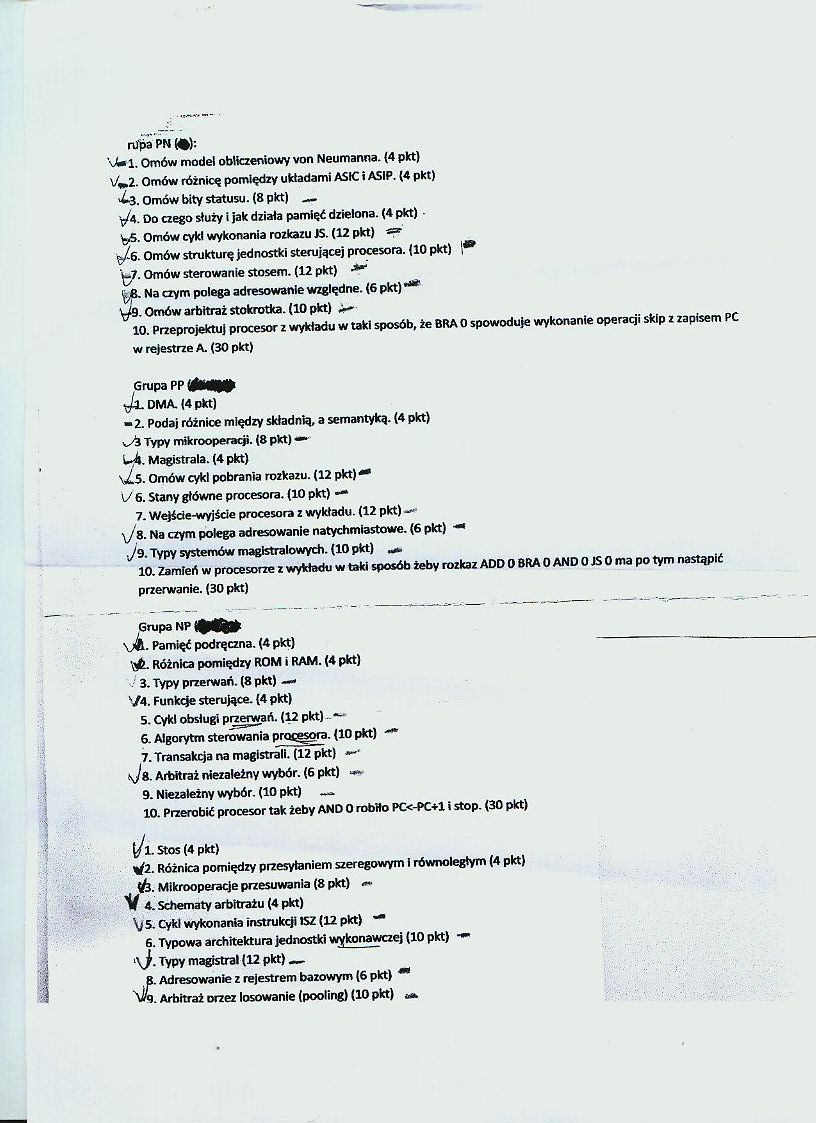

Egzaminy:

czerwiec 2011

Grupa NP

1. ISZ 0,sprawdzic, zapis akumulatora w pc (albo odwrotnie bo juz nie pamietam), kasowanie akumulatora, kasowanie sterowania

2. Pamięć podręczna

3. Mikrooperacja- wyjaśnić

4. Rodzaje przerwań- opisać

5. Adresowanie indexowe (opisać i gdzie jest używane)

6. Jednostka wykonawcza (typowa- opisac)

7. Mikrooperacje logiczne

8. Podać przerwanie w mikrooperacjach

wrzesień 2011

Grupa PP

1. Opisz schematy arbitrażu. (25pkt)

2. Opisz adresowanie względne i adresowanie natychmiastowe. (25pkt)

3. Zaprojektuj funkcję, która przywoła System Operacyjny. (25pkt)

4. Zaprojektuj operację PUSH i POP dla stosu, do którego będą zapisywane i odczytywane dane z rejestru A. (25pkt)

Poprzednie lata:

Termin 2, grupa NN: w nawiasach, ile dostałem pkt za odpowiedź, którą cytuję (za wyjątkiem 5, a 4 dodatkowo poprawiona)

1) opisać typy systemów magistralowych 25pkt (25pkt)

Magistrala - łącze multipleksowane w czasie.

Podziały:

*ze względu na kierunek transmisji danych:

jednokierunkowa (np. adresowa) dwukierunkowa (np. danych)

*ze względu na sposób transmisji:

szeregowa równoległa (szybsza, ale wymaga lepszej synchronizacji)

*typy systemów:

z jedną magistralą: procesor<>RAM<>urz. we/wy z dwiema magistralami: procesor<>RAM, procesor<>urz. we/wy z wieloma magistralami: procesor<>RAM, procesor<>układy we/wy, układy we/wy<>urządzenia we/wy

*magistrala systemowa najczęściej składa się z 3 magistral:

sterującej (jednokierunkowa, zarządzana przez procesor) adresowej (jednokierunkowa, zarządzana przez procesor) danych (dwukierunkowa)

2) opisać adresowanie indeksowe 8pkt (8pkt)

Wykorzystujemy rejestr indeksowy, w którym podana jest wartość przesunięcia.

Aby obliczyć adres efektywny, procesor musi dodać ją do argumentu rozkazu.

Adresowanie podobne do adresowania z rejestrem bazowym.

Tak, to wszystko;)

3) opisać układy arbitrażu 15pkt (15pkt)

Układ arbitrażu - urządzanie nadzorujące, służy do wyboru urządzenia które w danym momencie ma być nadrzędne.

Prosty przykład to arbitraż, gdzie procesor kolejno lub losowo przydziela urządzeniom dostęp do magistrali.

Rozwiązanie proste, ale mało efektywne, dlatego używa się specjalne układy arbitrażowe.

-arbiter przydziela dostęp urządzeniom w zależności od priorytetu, w ten sposób urządzenia wymagające częstszego dostępu lub szybszego dostępu częściej go otrzymują.

-arbiter otrzymuje żądania od urządzeń i na ich podstawie przydziela dostęp

-urządzenia same między sobą rozdzielają dostęp

-urządzenia wysyłają żądania, jeśli jest tylko jedno w danym czasie, uzyskuje dostęp, jeśli kilka, muszą ponowić żądanie.

4) sumowanie wektora, bez instrukcji ISZ, ale dodawanie ma autonastępnikowanie. 22pkt (5pkt)

Poprawione rozwiązanie:

ORG 30 (określamy, gdzie zaczyna się wykonywanie instrukcji)

20 50 (adres wektora liczb)

21 -n (długość wektora)

22 suma

…

30 CLA (zerujemy akumulator)

31 STA 22 (zapisujemy wartość sumy do M[22])

32 LDA 22 (wczytujemy wartość sumy częściowej)

33 ADD, *, +, 20 (adres argumentu zapisany w M[20], zwiększamy po wykonaniu rozkazu zawartość M[20])

34 STA 22 (zapisujemy sumę częściową)

35 LDA 21 (ładujemy M[21] do akumulatora)

36 INC (zwiększamy zaw. akumulatora)

37 STA 21 (zapisujemy M[21])

38 SZA 21 (sprawdzamy czy M[21] jest {już} zerem, jeśli tak, wykona się SKIP, jeśli nie, @39)

39 BRA 32 (skok do @32)

40 … (dalsze instrukcje)

…

50 dane

…

50+(n-1)

Moje rozwiązanie za mniej pkt:

ORG 30 (określamy, gdzie zaczyna się wykonywanie instrukcji)

20 50 (adres wektora liczb)

21 -n (długość wektora)

22 suma

…

30 CLA (zerujemy akumulator)

31 ADD, *, +, 20 (adres argumentu zapisany w M[20], zwiększamy po wykonaniu rozkazu zawartość M[20])

! ! !

32 INC 21 (zwiększamy zaw. M[21])

ten rozkaz jest bezadresowy,

trzeba odkładać dotychczasową sumę do M,

ładować do AC ilość pozostałych el.

po zwiększeniu zapisywać ją,

kolejnym przebiegu do AC ładować sumę częściową, itd.

33 SZA 21 (sprawdzamy czy M[21] jest {już} zerem, jeśli tak, wykona się SKIP, jeśli nie, @34)

34 BRA 31 (skok do @31)

35 … (dalsze instrukcje)

…

50 dane

…

50+(n-1)

5) dwie pamięci RAM: jedna użytkownika, druga systemowa. Dodany rejestr S. Napisać sterowanie. 30pkt (15pkt)

Spisałem się stronę A4 drobnym maczkiem, na pytanie czego brakuje odpowiedział: Cytat:

Wystarczyło napisać dwie instrukcje. Dwie linijki z mikrooperacjami. Zaakceptowałbym też rysunek z tym.

…

Tego już nie przytoczę, bo w porównaniu do poprzednich zadań to jest słoń wieloryb przy 4 mrówkach:D

====== Inne egzaminy u Sapiechy z ASK ======

I termin sprzed dwóch lat (wszystkie grupy):

NN (nie wszystkie pytania):

- co to jest magistrala.

- Zasada i dzialanie/budowa MMU

- organizacja pamieci wirtualnej

- adresowanie z rejestrem bazowym

- omowic typowe sterowanie procesora

- podac dla proca z wykladow: Cykl pobierania rozkazow.

PP:

1. BRA 0 → ma skoczyć do miejsca z rejestru A (pośrednio i bezpośrednio)

2. opisać sterowanie stosem

3. opisać RAM

4. napisać cykl ISZ

5. odwzorowawnie bezpośrednie adresu wirtualnego na rzeczywisty (schemat, opis)

6. omówić systemy magistralowe

7. wyjaśnić adresowanie natychmiastowe

8. omówić mikrooperacje przesyłania informacji

9. wyjaśnić pojęcie semantyka

NP:

1. ISZ 0 → w przypadku wykrycia 0 zamiast SKIP będzie wykonywał skok

względny o wartość zapisaną na mniej znaczącym bajcie

2. Omów mikrooperacje

3. Omów pamięć podręczną

4. Omów bity statusu

5. Omów odwzorowanie za pomocą pamięci TLB

6. Omów mikro0peracje logiczne

7. Tryb adresowania indeksowego

8. Typowa jednostka wykonawcza procesora

9. Dla procesora z wykładu podać obsługę przerwania.

PN:

1. rozkaz JS, adresowanie pośrednie, gdzie adres składa się z samych

jedynek ma wywołać pułapkę: zapisać zawartość akumulatora do rejestru

OUT i wywoływać przerwanie

2. omów typy przerwań

3. opisać ROM

4. napisać cykl JS

5. odwzorowanie pamięci CAM

6. omówić schematy arbitrażu

7. wyjaśnić adresowanie względne

8. omówić mikrooperacje arytmetyczne

9. wyjaśnić pojęcie składnia

==================

-0

-0

\\

Przy *_v2 przyjmujemy, że mamy połączenie pozwalające przypisać SP do MAR

(biorąc pod uwagę możliwe różnice w ilości bitów SP i MAR, chyba że przyjmiemy,

że są takiej samej wielkości - co jest raczej najbardziej sensowne).

\\

———————————————————————————————————

ZADANIE: Przeprojektuj procesor z wykładu tak , że BRA 0 spowoduje wykonanie operacji SKIP z zapisem PC w

rejestrze A.

\\

ROZWIĄZANIE:

Wprowadzamy dodatkowy przerzutnik MZ , do którego przez 16-wejściową bramkę or , podpinamy część MBR.

W cyklu pobrania rozkazu w t3, zapisujemy do niego wyjście bramki i go zamykamy. W tym przypadku wartość

rejestr MZ wygląda tak : MBR = 0 -